Produkter Kategori

- FM Transmitter

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV Transmitter

- 0-50w 50-1kw 2kw-10kw

- FM-antenne

- TV-antenne

- Antenne tilbehør

- Kabeler Stik Power Splitter Dummy Load

- RF Transistor

- Strømforsyning

- Audio Udstyr

- DTV frontend Udstyr

- Link System

- STL-system Microwave Link system

- FM-radio

- Power Meter

- Andre produkter

- Specielt til Coronavirus

Produkter Tags

Fmuser steder

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Afrikaans

- sq.fmuser.net -> albansk

- ar.fmuser.net -> arabisk

- hy.fmuser.net -> Armensk

- az.fmuser.net -> aserbajdsjansk

- eu.fmuser.net -> baskisk

- be.fmuser.net -> hviderussisk

- bg.fmuser.net -> Bulgarian

- ca.fmuser.net -> Catalansk

- zh-CN.fmuser.net -> Kinesisk (forenklet)

- zh-TW.fmuser.net -> Kinesisk (traditionelt)

- hr.fmuser.net -> Kroatisk

- cs.fmuser.net -> Tjekkisk

- da.fmuser.net -> dansk

- nl.fmuser.net -> Hollandsk

- et.fmuser.net -> estisk

- tl.fmuser.net -> filippinsk

- fi.fmuser.net -> finsk

- fr.fmuser.net -> Fransk

- gl.fmuser.net -> galicisk

- ka.fmuser.net -> Georgisk

- de.fmuser.net -> tysk

- el.fmuser.net -> Greek

- ht.fmuser.net -> haitisk kreolsk

- iw.fmuser.net -> hebraisk

- hi.fmuser.net -> hindi

- hu.fmuser.net -> Hungarian

- is.fmuser.net -> islandsk

- id.fmuser.net -> Indonesisk

- ga.fmuser.net -> Irsk

- it.fmuser.net -> Italiensk

- ja.fmuser.net -> japansk

- ko.fmuser.net -> koreansk

- lv.fmuser.net -> lettisk

- lt.fmuser.net -> Litauisk

- mk.fmuser.net -> Makedonsk

- ms.fmuser.net -> malaysisk

- mt.fmuser.net -> maltesisk

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> persisk

- pl.fmuser.net -> polsk

- pt.fmuser.net -> portugisisk

- ro.fmuser.net -> Romanian

- ru.fmuser.net -> russisk

- sr.fmuser.net -> serbisk

- sk.fmuser.net -> Slovakisk

- sl.fmuser.net -> Slovensk

- es.fmuser.net -> spansk

- sw.fmuser.net -> swahili

- sv.fmuser.net -> svensk

- th.fmuser.net -> Thai

- tr.fmuser.net -> tyrkisk

- uk.fmuser.net -> ukrainsk

- ur.fmuser.net -> Urdu

- vi.fmuser.net -> Vietnamesisk

- cy.fmuser.net -> walisisk

- yi.fmuser.net -> Jiddisch

PMOS og NMOS transistorer

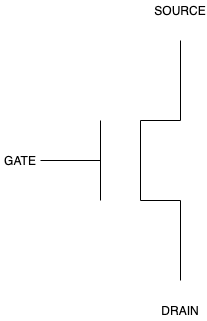

Mikroprocessorer er bygget af transistorer. De er især konstrueret af MOS-transistorer. MOS er et akronym for Metal-Oxide Semiconductor. Der er to typer MOS-transistorer: pMOS (positiv-MOS) og nMOS (negativ-MOS). Hver pMOS og nMOS er udstyret med tre hovedkomponenter: porten, kilden og afløbet.

For korrekt at forstå, hvordan en pMOS og en nMOS fungerer, er det vigtigt først at definere nogle udtryk:

lukket kredsløb: Det betyder, at elektriciteten strømmer fra porten til kilden.

åbent kredsløb: Dette betyder, at elektriciteten ikke strømmer fra porten til kilden; men snarere strømmer elektricitet fra porten til afløbet.

Når en nMOS-transistor modtager en ikke-ubetydelig spænding, fungerer forbindelsen fra kilden til drænet som en ledning. Elektricitet vil strømme fra kilden til afløbet uhæmmet - dette kaldes et lukket kredsløb. På den anden side, når en nMOS-transistor modtager en spænding på omkring 0 volt, vil forbindelsen fra kilden til drænet blive brudt, og dette omtales som et åbent kredsløb.

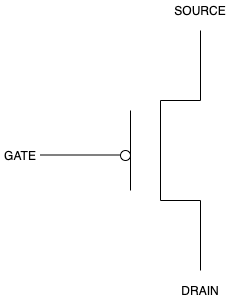

P-type transistoren fungerer nøjagtigt modsat n-type transistoren. Mens nMOS vil danne et lukket kredsløb med kilden, når spændingen er ikke ubetydelig, vil pMOS danne et åbent kredsløb med kilden, når spændingen er ikke ubetydelig.

Som du kan se på billedet af pMOS-transistoren vist ovenfor, er den eneste forskel mellem en pMOS-transistor og en nMOS-transistor den lille cirkel mellem porten og den første bjælke. Denne cirkel inverterer værdien fra spændingen; så hvis porten sender en spænding, der er repræsentativ for en værdi på 1, så vil inverteren ændre 1'et til 0 og få kredsløbet til at fungere i overensstemmelse hermed.

Da pMOS og nMOS fungerer på en modsat måde - på en komplementær måde - når vi kombinerer dem begge til et kæmpe MOS-kredsløb, kaldes det et cMOS-kredsløb, som står for komplementær metaloxid-halvleder.

Brug af MOS-kredsløbene

Vi kan kombinere pMOS- og nMOS-kredsløb for at bygge mere komplekse strukturer kaldet GATES, mere specifikt: logiske porte. Vi har allerede introduceret konceptet for disse logiske funktioner og deres tilhørende sandhedstabeller i den forrige blog, som du kan finde ved at klikke link..

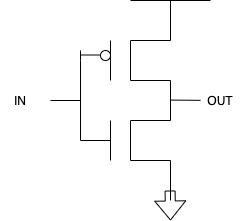

Vi kan tilslutte en pMOS-transistor, der forbinder til kilden, og en nMOS-transistor, der forbinder til jorden. Dette vil være vores første eksempel på en cMOS-transistor.

Denne cMOS-transistor virker på samme måde som den IKKE-logiske funktion.

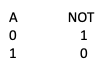

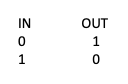

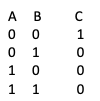

Lad os tage et kig på NOT-sandhedstabellen:

I NOT-sandhedstabellen er hver inputværdi: A inverteret. Hvad sker der med kredsløbet ovenfor?

Nå, lad os forestille os, at inputtet er 0.

0-tallet kommer ind og går både op og ned ad ledningen til både pMOS (øverst) og nMOS (nederst). Når værdien 0 når pMOS, bliver den inverteret til en 1; så forbindelsen til kilden er lukket. Dette vil give en logisk værdi på 1, så længe forbindelsen til jorden (drænet) ikke også er lukket. Da transistorerne er komplementære, ved vi, at nMOS-transistoren ikke vil invertere værdien; så den tager værdien 0 som den er og vil - derfor - skabe et åbent kredsløb til jorden (dræn). Således frembringes en logisk værdi på 1 for porten.

Hvad sker der, hvis et 1 er IN-værdien? Nå, efter de samme trin som ovenfor, bliver værdien 1 sendt til både pMOS og nMOS. Når værdien modtages af pMOS, bliver værdien inverteret til en 0; dermed er forbindelsen til KILDEN åben. Når værdien modtages af nMOS, bliver værdien ikke inverteret; værdien forbliver således en 1. Når en værdi på 1 modtages af nMOS, lukkes forbindelsen; så forbindelsen til jorden er lukket. Dette vil give en logisk værdi på 0.

At sætte de to sæt input/output sammen giver:

Det er ret nemt at se, at denne sandhedstabel er nøjagtig den samme, som den logiske funktion IKKE frembringer. Dette er således kendt som en IKKE-port.

Kan vi bruge disse to simple transistorer til at lave mere komplicerede strukturer? Absolut! Dernæst vil vi bygge en NOR-port og en OR-port.

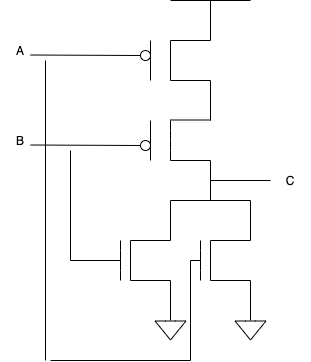

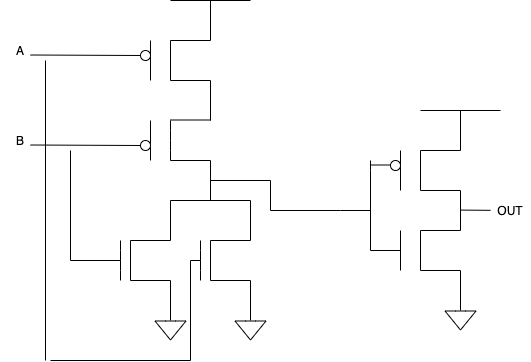

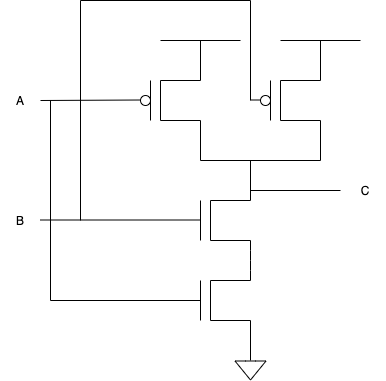

Dette kredsløb bruger to pMOS-transistorer i toppen og to nMOS-transistorer i bunden. Lad os igen se på input til porten for at se, hvordan den opfører sig.

Når A er 0, og B er 0, vil denne gate invertere begge værdier til et 1, når de når pMOS-transistorerne; nMOS-transistorerne vil dog begge bibeholde værdien 0. Dette vil få porten til at producere en værdi på 1.

Når A er 0, og B er 1, vil denne gate invertere begge værdier, når de når pMOS-transistorerne; så A vil ændre sig til 1 og B vil ændre sig til 0. Dette vil ikke føre til kilden; da begge transistorer kræver et lukket kredsløb for at forbinde input til kilden. nMOS-transistorerne inverterer ikke værdierne; så nMOS associeret med A vil producere et 0, og nMOS associeret med B vil producere 1; således vil nMOS forbundet med B producere et lukket kredsløb til jorden. Dette vil få porten til at producere en værdi på 0.

Når A er 1, og B er 0, vil denne gate invertere begge værdier, når de når pMOS-transistorerne; så A vil ændre sig til 0 og B vil ændre sig til 1. Dette vil ikke føre til kilden; da begge transistorer kræver et lukket kredsløb for at forbinde input til kilden. nMOS-transistorerne inverterer ikke værdierne; så nMOS, der er forbundet med A, vil producere et 1, og nMOS, der er forbundet med B, vil producere et 0; således vil nMOS forbundet med A producere et lukket kredsløb til jorden. Dette vil få porten til at producere en værdi på 0.

Når A er 1, og B er 1, vil denne gate invertere begge værdier, når de når pMOS-transistorerne; så A vil ændre sig til 0 og B vil ændre sig til 0. Dette vil ikke føre til kilden; da begge transistorer kræver et lukket kredsløb for at forbinde input til kilden. nMOS-transistorerne inverterer ikke værdierne; så nMOS associeret med A vil producere et 1, og nMOS associeret med B vil producere 1; således vil nMOS forbundet med A og nMOS forbundet med B producere et lukket kredsløb til jorden. Dette vil få porten til at producere en værdi på 0.

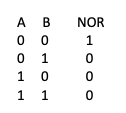

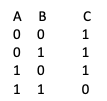

Portens sandhedstabel er således som følger:

I mellemtiden er den logiske NOR-funktions sandhedstabel som følger:

Vi har således bekræftet, at denne port er en NOR-port, fordi den deler sin sandhedstabel med den logiske NOR-funktion.

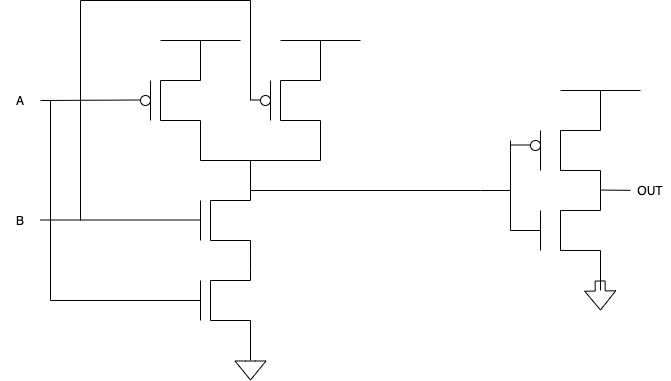

Nu vil vi sætte begge de porte, som vi har skabt indtil videre, sammen for at producere en OR-port. Husk, NOR står for IKKE ELLER; så hvis vi inverterer en allerede omvendt port, får vi originalen tilbage. Lad os afprøve dette for at se det i aktion.

Det, vi har gjort her, er, at vi har taget NOR-porten fra før og anvendt en NOT-port på udgangen. Som vi har vist ovenfor, vil NOT-porten tage en værdi på 1 og udsende en 0, og NOT-porten vil tage en værdi på 0 og udsende en 1.

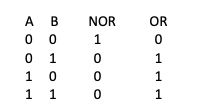

Dette vil tage værdierne af NOR-porten og konvertere alle 0'erne til 1'ere og 1'ere til 0'ere. Sandhedstabellen vil således være som følger:

Hvis du gerne vil øve dig mere i at teste disse porte, er du velkommen til at prøve ovenstående værdier for dig selv og se, at porten giver tilsvarende resultater!

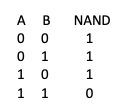

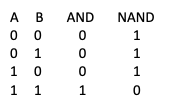

Jeg påstår, at dette er en NAND-gate, men lad os teste denne gates sandhedstabel for at afgøre, om det virkelig er en NAND-port.

Når A er 0, og B er 0, vil A's pMOS producere et 1, og A's nMOS vil producere et 0; således vil denne gate producere et logisk 1, da den er forbundet til kilden med et lukket kredsløb og afbrudt fra jorden med et åbent kredsløb.

Når A er 0, og B er 1, vil A's pMOS producere et 1, og A's nMOS vil producere et 0; således vil denne gate producere et logisk 1, da den er forbundet til kilden med et lukket kredsløb og afbrudt fra jorden med et åbent kredsløb.

Når A er 1, og B er 0, vil B's pMOS producere en 1, og B's nMOS vil producere en 0; således vil denne gate producere et logisk 1, da den er forbundet til kilden med et lukket kredsløb og afbrudt fra jorden med et åbent kredsløb.

Når A er 1, og B er 1, vil A's pMOS producere et 0, og A's nMOS vil producere et 1; så vi skal også tjekke B's pMOS og nMOS. B's pMOS vil producere et 0, og B's nMOS vil producere et 1; således vil denne gate producere et logisk 0, da den er afbrudt fra kilden med et åbent kredsløb og forbundet til jorden med et lukket kredsløb.

Sandhedstabellen er som følger:

I mellemtiden er den logiske NAND-funktions sandhedstabel som følger:

Vi har således verificeret, at dette faktisk er en NAND-port.

Hvordan bygger vi nu en OG-port? Nå, vi vil bygge en OG-port på nøjagtig samme måde, som vi byggede en OR-port fra en NOR-port! Vi tilslutter en inverter!

Da alt, hvad vi har gjort, er anvendt en NOT-funktion på en NAND-gates output, vil sandhedstabellen se sådan ud:

Igen, bekræft venligst for at sikre, at det, jeg fortæller dig, er sandheden.

I dag har vi dækket, hvad der er pMOS- og nMOS-transistorer, samt hvordan man bruger dem til at bygge mere komplekse strukturer! Jeg håber du fandt denne blog informativ. Hvis du kunne tænke dig at læse mine tidligere blogs, finder du listen herunder.